DESIGN WORKFLOW AUDITOR POINT SOLUTIONS*

Yotta has two types of design workflow auditors. The first is a suite of command line point tools. On an as-needed basis, they can be manually invoked at key interchange points throughout the design flow.

The second is a single cloud-based solution, It reports the developing state of all of the data within the design workflow including all cross-format cell dependencies.

Here, we'll introduce our point solutions which have the same ability to report changes at all levels of design hierarchy to the leaf cell layer level.

There are several workflow interchanges where there is significant opportunity to lose track of what is in a design even with the latest PLM, configuration and data management systems.

. . . PDK releases to Fabless/System OEMs/3rd Party IP Suppliers

. . . Standard cell library development and releases to 3rd party IP supplier design project teams

. . . Standard cell library releases to Fabless/System OEM/IDM design project teams that include internally developed IP and IP developed and released by 3rd parties

. . . Structured Net List, Floor Plan and standard cell library releases to layout integration/Tapeout

Yotta's technology has solutions for each of theses interchanges.

. . . IP Library Release Auditor

. . . IP Library Release Reporter

. . . Tapeout Auditor

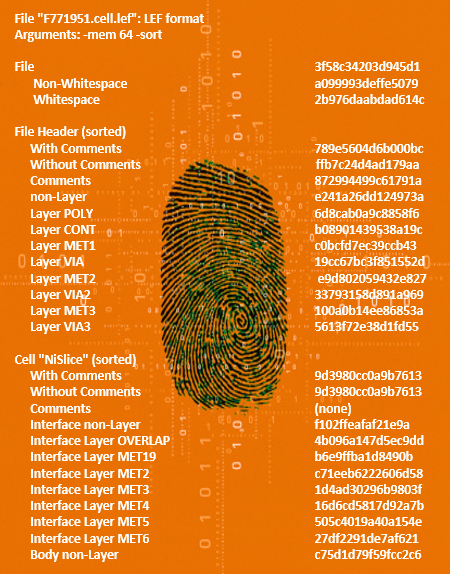

Yotta's Smart Signature Point Tools can address all of the cell views in various interchange formats (SPICE, Liberty, LEF, GDSII, Verilog, VHDL, DEF, OASIS).

As well, Yotta has a smart-signature-inspired fast-XOR layout equivalence checking tool. It is faster than an XOR by 100X. It does not discard data nor does it flatten the data. It reports differences cell-by-cell. It can be used as new GDSII and OASIS EDA readers and writers are qualified for production.

The remaining Smart Signature design workflow audit tools check for IP ownership, warranty issues, licensing and IP royalty payment needs. They require more enterprise information to be useful such as the owners of IP, which IP can be modified without authorization, etc.

. . . IP Identity Manager

. . . IP Ownership Manager

. . . Hard IP Royalty Auditor

. . . IP Warranty Auditor

Once a customer has installed the first three point tools, it'll be relatively easy to add parameters to the database that check of warranty and ownership matters.

Request more Information

Yotta's Design Workflow Auditing Capability spans the semiconductor factory to design workflow from SDK releases through their acceptance and use by 3rd Party IP suppliers and Fabless/IDM/System OEM design houses.

Tapeout

In-place Optimization

Layout Integration

Block-level Design

Floorpanning

Logic Design/Synthesis

System-level Design

Library Release Reporter

Library Development

Master Siganture Database

Fabless

IDM

System OEM

3rd Party IP

Manufacturing

Process Development

PLM / Configuration / Data Managment

SPICE / Liberty / LEF / GDSII / OASIS / Verilog / VHDL / DEF / Warranty / Licensing / Ownership / Identity

Key Cell View Integrity Signature Generation and Audit Points

PDK Release

Signature Generation

smart-XOR layout equivalence checking

OASIS/GDSII

Hard IP Royalty Audit

Cell View Dependencies

PDK

. . . SPICE models, Design Rules, Circuit Extraction Parameters

Library Development

. . . SPICE, Liberty, LEF, GDSII, OASIS

Logic Design / Synthesis

. . . Verilog, VHDL, Liberty

Floor Planning

. . . Verilog, VHDL, DEF

Layout Integration

. . . Liberty, LEF, GDSII, OASIS, DEF

Tapeout

. . . GDSII, OASIS

"... The Company's technology plays a substantial role helping us isolate and fix problems before they become silicon issues ..."

Lisa Fisher

Engineering Manager

Texas Instruments

API

OAS = OASIS

GDS = GDSII

Workflow Auditor Point Tools

TM

®

© Getty Images

* US Patents 9,122,825, 8,555,219, 8,266,571 and 7,685,545.

International Patents: China 200980129771.8, Japan 4768896, Korea 10-1580258, Israel 209907. Pending Applications filed with the European Patent Office (EPO)

NEW at Yotta Data Sciences

OASIS® is a Registered Trademark of Thomas Grebinski

© 2008-2024 Yotta Data Sciences, Inc. All rights reserved.

February 16, 2024- Yotta is offering, to qualified partners, a six-month evaluation-period, with support, for its SEMI P39-0416 OASIS Reader/Writer Source Code.

Visit Page: OAS Reader/Writer

Visit Page: OAS Source Code