DESIGN VIEW IN A CLOUD*

At the leading edge of semiconductor technology, the view of a factory to design workflow is not as clear is it can be. Data within this workflow is managed through configuration and data management systems, sometimes stand-alone or integrated into a Product Lifecycle Management (PLM) platform. The view is at the file level in which there can be tens of thousands of unique cells and billions of cell placements. There is not a higher level dynamically referential view of the content of the file as it develops. If a change occurs within any cell, a designer cannot ask for a roll-up of that cell describing all of the data that had been used to create it and what had changed, where, relative to the cell the designer actually has in use which, by the way, might not be the correct version of the cell. In other words, project teams use configuration and data management systems as a means to manage its design files so to have the greatest possibility that what they have in use is correct.

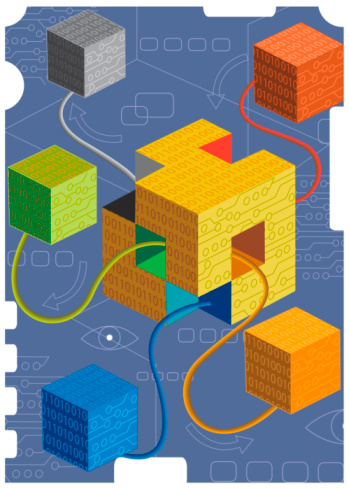

At the leading edge of semiconductor technology, the workflows are globalized. They involve many parties as well. A Foundry to Fabless flow can include 3rd party IP Suppliers. The Foundry supplies PDKs to both who use the PDKs to build their libraries of standard cell views in Liberty, LEF, GDSII and OASIS. The 3rd Party IP suppliers supply their standard cell libraries to the Fabless companies. They, in turn, release both to their internal project teams who design ICs at the block and chip levels. Their designs are released to the foundries for mask generation and test. Hundreds to thousands of people can be involved in what can be a $200M design effort.

Yotta can bring a higher level view of a globalized collaborative effort like this together so that people can make more informed and aggressive decisions knowing that the information they have to work with is up to date - backed by an audited trail of decisions and data in use at the time back to the first PDK release.

The view will be at the leaf cell level through all levels of design hierarchy (tapeout). We produce smart signatures at key points throughout the workflow such as PDK, Library development and release (SPICE, Liberty, LEF, GDSII, OASIS), System-level design (Verilog, VHDL), Logic Design and Synthesis (Liberty, Verilog, VHDL), Floor Planning (Verilog, VHDL, DEF), Layout Integration (Liberty, LEF, GDSII, OASIS, DEF), In-Place Optimization (the same) and Tapeout (OASIS, GDSII). We track the development (the versioning) of these lower-level views and their dependencies. As changes occur, we report what and where they had occurred. We'll be able to detect whether a cell in use is not correct and it location throughput the design's hierarchy and the number of instances.

Yotta's technology resides atop existing configuration and data management systems. It does not divert the workflow. It merely peers into the data that is there to create the indexes and generate the signatures. The signatures from the Foundry, Fabless and 3rd Party IP Suppliers are loaded into a cloud. Yotta's database software manages the versioning of the lower-level cell views as they occur. Those subscribing to the cloud Software-As-A-Service (SaaS) will have access to a roll-up of the current state of their design in real time.

This will prevent design errors caused by the use of the wrong cell views. The attempts to use them will be detected and reported the moment of the detection. As important, this higher-level view of the factory to design flow will be clearer in its understandability. Collaborative teams should be able to learn more quickly about what it is that is needed to take the next steps within this very complex, large and sophisticated ecosystem. Designers will be able to develop a better understanding of the relationships between the raw data and the factory and the abstracted views of the factory they have in use. It'll be as though the factory team and all of that raw data is just down the hall. Designers will be able to design more abrasively / feedback to the foundries will be more accurate / the abstracted views of a factory's manufacturing flow will become more accurate, and telling, with time. Warranty issues, lost IP, opportunities for IP theft and mistakes made inadvertently by humans and machines will be caught much earlier in the flow.

"... The Company's technology plays a substantial role helping us isolate and fix problems before they become silicon issues ..."

Lisa Fisher

Engineering Manager

Texas Instruments

SaaS

Signature Cloud

Master Database

Process Development

PDK

Smart Signatures

Tapeout

In-Place Optimization

Layout Integration

Floor Planning

Logic Design/Synthesis

System Level Design

Library Development/Release

Smart Signatures

Library Development/Release

System Level Design

Logic Design/Synthesis

Floor Planning

Layout Integration

In-Place Optimization

Standard Cell Library Release

PDK

Post-tapeout audit

Warranty

Licensing

IP Ownership

IP Royalty

3rd Party IP

IDM/Fabless/System OEM

The cloud can be on-premise or serve a larger collaborative ecosystem such as a Fabless company's Foundries and IP suppliers. Larger still is to elect to be part of an industry collaborative signature cloud.

The next steps are to tie embedded (C++), manufacturing and test code and data to design. Hopefully to the cell level.

PLM / Configuration / Data Managment

SPICE / Liberty / LEF / GDSII / OASIS / Verilog / VHDL / DEF / Warranty / Licensing / Ownership / Identity

Signature

Generation

To Cloud

Manufacuring

Cell View Dependencies

PDK

. . . SPICE models, Design Rules, Circuit Extraction Parameters

Library Development

. . . SPICE, Liberty, LEF, GDSII, OASIS

Logic Design / Synthesis

. . . Verilog, VHDL, Liberty

Floor Planning

. . . Verilog, VHDL, DEF

Layout Integration

. . . Liberty, LEF, GDSII, OASIS, DEF

Tapeout

. . . GDSII, OASIS

OAS = OASIS

GDS = GDSII

Workflow Auditor Point Tools

TM

®

© Getty Images

NEW at Yotta Data Sciences

* US Patents 9,122,825, 8,555,219, 8,266,571 and 7,685,545.

International Patents: China 200980129771.8, Japan 4768896, Korea 10-1580258, Israel 209907, European Patent 2310967.

OASIS® is a Registered Trademark of Thomas Grebinski

© 2008-2024 Yotta Data Sciences, Inc. All rights reserved.

February 16, 2024- Yotta is offering, to qualified partners, a six-month evaluation-period, with support, for its SEMI P39-0416 OASIS Reader/Writer Source Code.

Visit Page: OAS Reader/Writer

Visit Page: OAS Source Code